Overview

The following article covers how Dream Chip implemented a multipolicy SoC RTL linting sign-off methodology using Real Intent Ascent Lint to improve engineering verification time while maintaining coverage.

To see the original case study, please visit: https://www.realintent.com/multipolicy-soc-linting-methodology/

Challenge: SoC RTL Linting Sign-Off across IP Developed Under Different Coding Standards

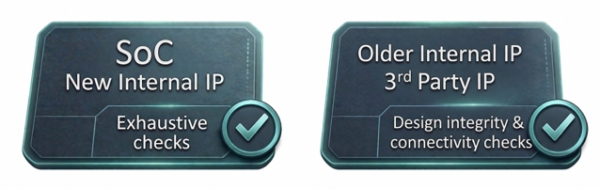

Dream Chip's SoCs incorporate a wide variety of internal and third-party IP developed under different coding rules – each requiring distinct criteria for RTL linting sign-off. Recently developed IP typically requires exhaustive rule checking, while pre-existing IP often needs only foundational design integrity and connectivity validation.

This disparity created a challenge for full-SoC RTL linting sign-off. Applying a single master ruleset across all IP generates excessive noise in violation reports – reviewing the extra violations and applying waivers consumes significant engineering time.

The alternative, black-boxing some IP, risks missing critical issues such as connectivity problems. Basic design integrity checks are especially valuable for IP that the team is less familiar with.

Black-boxing some IP risks missing issues such as connectivity

Dream Chip needed a more efficient approach to full-SoC RTL linting sign-off that could accommodate this heterogeneity without sacrificing coverage.

Dream Chip's Multipolicy RTL Linting Sign-Off Methodology

Dream Chip structured its approach to address three categories of rule policies within a single RTL linting sign-off run.

- Master SoC policies – these cover all current SoC guidelines and are aligned with coding rules for synthesizable code. Newer IP is developed under these guidelines.

- Older internal IP policies – select rules from the master ruleset that conflict with legacy development guidelines are disabled, such as specific naming styles.

- 3rd-party IP policies – naming conventions and certain design guidelines are disabled in areas where Dream Chip lacks full visibility, while critical rules remain enabled. One example is that checks for multiple driven wires remain mandatory because such violations indicate either an incorrect IP configuration or a defect in the IP itself.

Dream Chip's methodology with Real Intent Ascent Lint consists of four elements:

- Establishing a master SoC-level policy to serve as a superset of all rules.

- Applying the master ruleset to the SoC level and for newer internal IP.

- Disabling specific policy subsets for older internal IP and/or 3rd-party IP.

- Run Ascent Lint multipolicy RTL linting sign-off.

Design Hierarchy: How Policy Inheritance Works

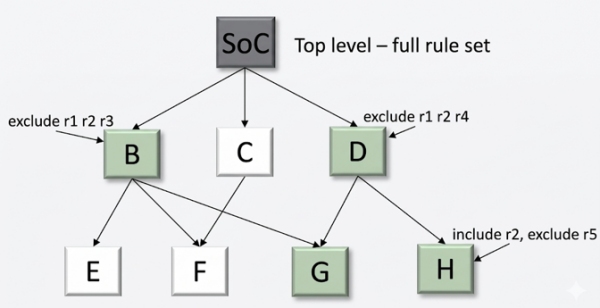

The diagram below shows a representative design hierarchy. At the SoC top-level, the full rule set is enabled. IP modules B, C, and D are instantiated below, each with locally defined rule inclusions and exclusions.

A key principle: any policy set at the top of a subsystem is automatically inherited throughout that portion of the hierarchy.

- Module B excludes rules r1, r2, and r3 – these restrictions propagate down to modules E, F, and G.

- Module D excludes rules r1, r2, and r4 – which are then inherited by modules G and H. Module G therefore has r3 also disabled due to its position within the hierarchy under Module B.

- Module H overrides its inherited policy by re-including r2 and excluding r5, ultimately resulting in rules r1, r4, and r5 being disabled for that specific block.

Dream Chip’s typical IP rule policy customizations filter out stylistic rules while prioritizing structural connectivity, clock, and reset checks — preserving the checks that matter most for integrity.

Identifying a Bit Width Mismatch in Wrongly Configured IP

The multipolicy RTL linting approach enabled Dream Chip to identify a bit width mismatch error in IP that had been configured with incorrect parameter settings.

Errors of this type may not be detected when IP is verified in isolation, rather than in the precise configuration used within the SoC integration context.

Dream Chip also achieved a 5X improvement in simulation run time and turnaround time for verifying all data paths, by organizing data path modeling files by their specific function.

Result: A Single RTL Linting Sign-Off Run Across All Rule Policies

Dream Chip’s low noise multipolicy SoC linting methodology with Ascent Lint delivered several concrete improvements.

1. Comprehensive Coverage: One full SoC-level run now finds all issues across the entire design hierarchy.

2. Streamlined Updates: When any IP is updated, a single run replaces what previously required separate runs with different rule sets.

3. Noise Reduction: Noise is significantly reduced without sacrificing coverage. Checking third-party IP under the master ruleset previously generated hundreds of false violations that engineers had to review and waive. Connectivity and basic design integrity checks are still enforced throughout.

4. Continuous RTL Linting: Additional errors can be identified efficiently through Jenkins checks running in the background, triggered either by design updates or at defined time intervals.

Dream Chip reported that Ascent Lint’s multipolicy linting runtime was only 16 minutes for the full SoC, which includes several processors.